СИСТЕМА КОМАНД ПРОЦЕССОРОВ СЕМЕЙСТВА PDP

В качестве примера реально существующего процессора, удобного для более детального изучения, возьмем процессор серии машин, созданных фирмой DEC (США) и известных под названием PDP-11 (в нашей стране аналогичные процессоры использовались в семействах 16-разрядных мини- и микро-ЭВМ «Электроника», ДВК, БК, а также в школьном компьютерном классе УКНЦ; всего таких машин было выпущено в СССР до 1,3 млн. штук и примерно столько же в США). Это семейство мини- и микро-компьютеров - одно из самых долгоживущих: первая машина этой серии была выпущена в 1970 г., а прекращение выпуска было запланировано фирмой DEC на 1997 г.

Причина выбора процессора PDP для иллюстрации обсуждаемого вопроса состоит в том, что система команд этого процессора построена на простых и наглядных принципах, изучив и запомнив которые уже можно составлять несложные программы. В то же время система команд других процессоров, например, широко распространенных представителей семейства «Intel», устроена значительно сложнее, требует запоминания большого количества справочных данных. В качестве подтверждения сказанного достаточно указать, что в команде процессора PDP может быть использован любой из имеющихся внутренних регистров, тогда как многие команды процессоров «Intel» оперируют с фиксированными регистрами, не допуская альтернативного расположения данных и результатов.

Процессор машин серии PDP и его отечественные аналоги (при дальнейшем изложении будем все это обширное семейство для краткости называть «процессор PDP») с точки зрения программиста устроен довольно просто. Он состоит из восьми регистров общего назначения (РОН) и особого регистра, в котором отображается текущее состояние процессора (в иностранной литературе его принято обозначать PSW - Processor Status Word). Любой из регистров общего назначения может быть использован в командах на равных основаниях. Вместе с тем имеются два выделенных регистра, содержимое которых процессор использует для собственных нужд. Прежде всего следует назвать регистр R7, выполняющий роль счетчика команд, в котором хранится адрес следующей инструкции программы.

Другим выделенным регистром является указатель стека R6, используемый при запоминании информации в момент вызова подпрограмм и при переходе к обработке прерывания.

Остальные 6 регистров, обозначаемые RO, Rl. R2, R3, R4, R5, программист может полностью использовать по своему усмотрению. Имеется только одно (непринципиальное) исключение: в обширной системе команд PDP существует лишь единственная, и то достаточно экзотическая, команда (MARK), работающая с регистром R5.

Следует отметить, что и выделенные регистры процессора R6 и R7 могут быть использованы в любой команде наряду с обычными РОН RO-R5. Например, допускается переписать информацию из R7 в R3 и тем самым сообщить программе адрес памяти, в котором находится следующая команда программы. Такой прием очень часто используется программистами для автоматической «самонастройки» на те адреса ОЗУ, в которых оказалась загруженной программа. Интересно, что такого простого доступа к содержимому программного счетчика многие процессоры не имеют.

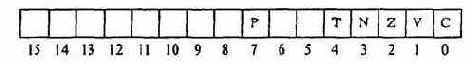

Рис. 4.14. Схема регистра состояния процессора PDP

Регистр состояния процессора PSW, как и все РОН, является 16-битным. Его особенностью является то, что каждый его бит имеет самостоятельное значение и может использоваться процессором отдельно от других. В управляющих битах регистра постоянно отображается информация о выполняемых результатах (отрицательность, равенство нулю и т.п.), а также о состоянии процессора в данный момент (например, один из битов позволяет разрешать или запрещать обработку прерывании). Из всех используемых битов (не все 16 бит регистра состояния задействованы!) наиболее используемы два; их принято обозначать N и Z. Управляющий признак N (Negative) отражает знак результата операций: если число отрицательное, то N = 1, неотрицательное - N = 0. Бит Z (Zero) говорит о равенстве или неравенстве нулю результата: в первом случае Z = 1, во втором - Z = 0. Путем несложных рассуждений можно убедиться в том, что из шести известных математических соотношений

=, < , > , ? , ? , ?

четыре могут быть проанализированы по одному из признаков, а два оставшихся требуют совместного анализа битов N и Z.

Другие управляющие биты, изображенные на рисунке, используются следующим образом. Бит Р - задание маскировки прерываний от внешних устройств (Р = 0 -прерывание состоится. Р = 1 - замаскировано). Бит Т - «признак ловушки»; при Т = 1 после прерывания запускается специальная системная программа, позволяющая на этапе отладки текущей программы осуществлять режим трассировки. Бит V -признак переполнения разрядной сетки при арифметической операции (если это произошло, устанавливается V = 1); бит С - аналогично при переполнении разрядной сетки при логической операции, сопровождаемой сдвигом кода. Описанные управляющие признаки широко используются для реализации разветвлений программы в зависимости от полученных результатов, анализа причин прерываний и других действий.

Процессор PDP имеет достаточно удобный и широкий набор команд. Основная их часть является двухадресными и одноадресными, т.е. они обрабатывают два или один операнд, соответственно. Для выполнения некоторых управляющих команд данные не требуются (например, команда остановки программы) - такие команды не содержат ссылок на операнды. Форматы одно- и двухадресных команд изображены ниже на рис. 4.15.

|

КОП |

КМА |

N POH |

||

|

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

||||

|

КОП |

KMA1 |

N POH1 |

KMA2 |

N POH2 |

|

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

||||

Рис.4.15. Формат одноадресной команды (вверху) и двухадресной (внизу). КОП - код операции. КМА - код метода адресации, N РОН - номер регистра общего назначения (код адреса)

Примеры некоторых наиболее важных операций приведены в табл. 4.2. Действия, выполняемые по простейшим арифметическим операциям, понятны из пояснений.

В некоторых дополнительных пояснениях нуждаются только команды переходов.

Во-первых, переходы

бывают абсолютные (на заданный адрес) и относительные (на определенное число команд относительно данной). Переходы первого типа более наглядны и могут быть реализованы на любой адрес ОЗУ. Относительные переходы требуют вычисления адреса перехода, зато они не привязаны к конкретным адресам ОЗУ: программа, использующая относительные переходы, может работать в любом месте памяти. Относительные переходы занимают меньше места в памяти, чем абсолютные; вследствие этого диапазон относительных переходов ограничен (в процессоре PDP только на 127 слов вперед и 128 - назад).

Таблица 4.2

Наиболее важные команды процессора PDP

|

Мнемоника команды |

Содержание команды |

Пояснения |

|

HLT |

Остановка |

Выполнение программы прекращается |

|

CLR А |

Очистить А |

А:=0 (в операнд А засылается 0) |

|

INC А |

Увеличить А на 1 |

А:=А+ 1 (значение А увеличивается на 1) |

|

DEC A |

Уменьшить А на 1 |

А:=А-1 (значение А уменьшается на 1) |

|

MOV А,В |

Переписать А в В |

В:=А (В принимает значение А) |

|

ADD A,B |

Сложить А в В |

В:=А + В (сумма помещается в В) |

|

SUB A,B |

Вычесть А из В |

В:=В-А (разность помещается в В) |

|

СМР А,В |

Сравнить А с В |

По знаку разности А-В устанавливаются |

|

Управляющие биты; А и В сохраняются |

||

|

JMP А |

Безусловный переход к А |

Безусловный переход по адресу А |

|

BR К |

Безусловный переход на К. слов |

Безусловный переход через К команд |

|

BEQ К |

Переход по = 0 |

Переход на К слов, если результат = 0 |

|

BNE К |

Переход по ? 0 |

Переход на К слов, если результат ? 0 |

|

BPL К |

Переход по ? 0 |

Переход на К слов, если результат ? 0 |

|

ВМ1 К |

Переход по < 0 |

Переход на К. слов, если результат < 0 |

|

JSR А |

Вызов подпрограммы по адресу А |

Переход на адрес А с запоминанием адреса возврата для команды RET |

|

RET |

Возврат из подпрограммы |

Возврат на команду, следующую за вызовом подпрограммы |

Во-вторых, переходы делятся на безусловные и условные. Безусловные, как. следует из названия, происходят всегда. При выполнении условного перехода анализируются управляющие биты. Переход происходит только в том случае, когда признаки имеют требуемые значения; в противном случае переход игнорируется и выполняется следующая за ним команда. Чаще всего условному переходу предшествует команда сравнения, «подготавливающая» управляющие признаки для анализа. Отметим, что команды BEQ и BNE проверяют значение признака Z, a BPL и BMI -признака N.

В таблице у команд перехода для наглядности указаны адреса или величина смещения в словах. Именно таким образом и кодируются команды в памяти ЭВМ. Однако при записи текстов программ дело обычно обстоит несколько проще: в требуемых местах программы ставятся метки, а расчет конкретных адресов и смещений машина производит самостоятельно (см. приводимые ниже примеры).

В приведенных в таблице командах в качестве операндов фигурируют условные обозначения А и В. Расшифруем их. Система команд процессора PDP построена достаточно логично и закономерно, поэтому любой операнд- и первый, и второй - в любой операции задается совершенно одинаково. В PDP существует 8 различных способов задать местонахождение информации, требующейся для выполнения операции. Их принято называть методами адресации, и все они связаны с различным использованием РОН. Наличие развитой системы методов адресации делает программирование для процессора PDP очень гибким и мощным.

Опишем коротко организацию основной памяти, контролируемой обсуждаемым микропроцессором. Основная адресация - байтовая; каждый байт имеет уникальный адрес. Так как процессор является 16-разрядным, то объем контролируемого им номинально адресного пространства 64 кбайта; на деле программисту для размещения программы и данных доступно меньшее пространство, так как 8 кбайт памяти зарезервировано для общения с внешними устройсгвами. Реально, однако, с помощью специальных механизмов преобразования исполнительных адресов емкость ОЗУ, доступную пользователю, делают значительно большей (детали рассматривать не будем).

Байт может быть операндом для некоторых команд. Однако, большая часть команд обрабатывает операнды длиной 2 байта - «слово». Слово состоит из двух соседних байтов; адресом слова считается адрес младшего входящего в него байта.

Таблица 4.3

Некоторые способы указания операндов в командах

|

Название |

Мнемоника |

Пояснение |

|

Регистровая Косвенно-регистровая Автоинрементная Автодекрементная |

Rn (Rn) (Rn)+ -(Rn) |

Операнд в регистре Rn Операнд в ячейке ОЗУ, адрес которой в Rn То же, но после чтения Rn увеличивается на 1 То же, но перед чтением Rn уменьшается на 1 |

В качестве иллюстрации разберем выполнение команды MOV(R1)+,RO

По этой команде сначала считывается информация из памяти по адресу, находящемуся в R1. После чтения значение R1 автоматически увеличивается, так что при последующем выполнении данной команды будет обрабатываться следующая ячейка. Операция завершается записью считанной из ОЗУ информации в регистр R0.

Из разобранного примера отчетливо видно, что имеющиеся у процессора PDP способы адресации позволяют удобно работать не только с одиночными данными, но и с массивами последовательно хранящейся в памяти информации. Кроме того, некоторые приемы использования счетчика команд R7 в качестве РОН могут давать еще более интересные эффекты. Пусть, например, в некоторой программе встречается команда

MOV (R7) + , R2

и в следующем за ней слове хранится число 6. Учитывая, что после извлечения команды из ОЗУ счетчик R7 немедленно увеличивается, в момент выполнения команды его содержимое уже показывает на слово памяти, где хранится число 6. Следовательно, в качестве операнда (R7) будет считано именно оно, и, кроме того, R7 автоматически «передвинется» на следующую за константой ячейку благодаря автоинкрементному способу адресация. Таким образом, описанный прием позволяет использовать в качестве операнда константу, хранящуюся непосредственно в команде. Завершая обсуждения основных принципов программирования процессора PDP.

приведем примеры линейного, разветвляющегося и циклического фрагмента программы.

Пример I.

Программа вычисления по формулам R1:=R2+R3; R4:=R3-R2.

Программа 131

MOV R2, Rl ; сразу складывать нельзя, так как сумма заменяет

;второй операнд

ADD R3, Rl

MOV R3, R4

SUB R2, R4

HLT

Пример 2. В Rl и R2 хранятся некоторые числа. Поместить большее из них в R5, а меньшее-в RO.

Программа 132

СМР Rl, R2 ;сравнить Rl и R2

BPL L1 ;переход при R1?R2, если R2>R1

MOV Rl, R0

MOV R2, R5

BR L2

;если R1>R2

LI: MOV Rl, R5

MOV R2, R0

L2: HLT

Примечание. В тексте программы указаны переходы на метки, но в результате трансляции они будут автоматически преобразованы в переходы через заданное число слов.

Пример 3. Пусть в Rl задан начальный адрес массива ОЗУ, а в R2 - число ячеек в нем. Вычислить сумму элементов массива.

Программа 133

CLR R0 ;очистка суммы

LI: ADD (Rl) + , R0 ;добавить к сумме очередной элемент

DEC R2 ;уменьшить на единицу число оставшихся элементов

BNE L1 ;цикл, пока не останется 0 элементов

HLT

Примечание. В программе используется тот факт, что команда DEC автоматически сравнивает результат с нулем, что делает ненужной специальную команду сравнения СМР.